# Fixed Width Booth Multiplier using Error Compensation

Abraham George, Prof. Binu K. Mathew

**Abstract**— In many multimedia and digital-signal processing (DSP) applications, multipliers are considered to be the basic arithmetic units. These multipliers significantly influence the system's performance and power dissipation. To achieve high performance, the modified Booth encoding has been widely adopted in parallel multipliers. It reduces the number of partial products through performing multiplier re-coding. The number of adder cells in the Booth multiplier architecture can be reduced by various techniques. The process of truncation can be done so that the multiplier structure can be simplified to form a fixed width multiplier. The *2n* bit product that is to be obtained from the multiplication of *n* bit multiplicand and *n* bit multiplier is truncated to *n* output bits by eliminating the adder cells needed for the addition of *n* least-significant bits (LSBs). The elimination of certain adder cells can cause truncation error. Hence, appropriate compensation biases are to be introduced into the retained adder cells. The compensation circuit needed for reducing truncation error is also designed here. Our proposed encoder was simulated in Mentor Graphics Model Sim 10.1c, using Verilog HDL. The output of the encoder was synthesized using Leonardo Spectrum. The synthesis results show that the critical path delay as well as the total number of gates is reduced when compared with the prevailing technology.

Index Terms— Booth multiplication, Radix-4, modified Booth multiplication, carry save adder, carry look ahead adder, Booth encoder, partial product matrix.

## **1** INTRODUCTION

ow power dissipation, area minimization and improved processing performance are the major factors of concern in many multimedia and digital signal processing (DSP) systems. Multipliers can be considered to be the fundamental arithmetic unit in these systems and they can influence the system performance and power dissipation significantly. To achieve high performance, the modified Booth encoding which reduces the number of partial products through performing the multiplier recoding has been widely adopted in multipliers [1]-[3]. Moreover,  $n \times n$  fixed-width multipliers that generate only the *n* most significant product bits are frequently utilized to maintain a fixed word size such that significant hardware complexity reduction and power saving can be achieved. This is made possible by directly removing the adder cells of standard multiplier for the computation of the nleast significant bits of 2n-bit output product. However, a huge truncation error will be introduced to this kind of directtruncated fixed-width multiplier (DTFM).

To effectively reduce the truncation error, various error compensation methods, which add estimated compensation value to the carry inputs of the reserved adder cells, have been proposed. The error compensation value can be produced by the constant scheme or the adaptive scheme. The constant scheme [4], [5] pre-computes the constant error compensation value and then feeds them to the carry inputs of the retained adder cells when performing multiplication operations regard-

less of the influence of the current input data value. With the advantage of simplification, the truncation error of the constant scheme is relatively large. On the contrary, the adaptive scheme [6]-[8] was developed to achieve higher accuracy than the constant scheme through adaptively adjusting the compensation value according to the input data at the expense of a little higher hardware complexity. However, most of the adaptive error compensation approaches are developed only for fixed-width array multipliers and cannot be applied to significantly reduce the truncation error of fixed-width modified Booth multipliers directly. To overcome this problem, several error compensation approaches [9]-[11] have been proposed to effectively reduce the truncation error of fixed-width modified Booth multipliers. In certain approaches, the compensation value was generated by using statistical analysis and exhaustive simulation analysis.

In this project work, an error compensation circuit for the fixed-width modified Booth multiplier with higher accuracy and simpler hardware structure is proposed. To obtain better performance with a simple error compensation circuit, Booth encoded outputs are utilized to generate the error compensation value. To accomplish this goal, a simple compensation circuit composed of simple logic gates is developed according to the proposed error compensation function. Simulation and implementation results show that the proposed fixed-width modified Booth multiplier actually achieves much higher performance than existing fixed-width modified Booth multipliers [12].

This paper is organized as follows. In section II the modified Booth multiplier fundamentals are reviewed. Section III deals with the proposed Booth encoder circuit. Section IV deals with the results obtained from the simulation and synthesis. Finally, section V concludes the paper.

<sup>•</sup> Abraham George is currently working as Assistant Professor in Saintgits College of Engineering, Kottayam.. E-mail: abraham.george@saintgits.org

Prof. Binu K. Mathew is currently working as Associate Professor in Saintgits College of Engineering, Kottayam.

International Journal of Scientific & Engineering Research Volume 4, Issue 8, August-2013 ISSN 2229-5518

#### **2 FUNDAMENTAL OF MODIFIED BOOTH MULTIPLIER**

Signed multiplication is a careful process. With unsigned multiplication, there is no need to take the sign of the number into consideration. However in signed multiplication, the same process cannot be applied because the signed number is in a 2's complement form which would yield an incorrect result if multiplied in a similar fashion to unsigned multiplication. In this case Booth's algorithm [13] can be used since it preserves the sign of the result. Booth multiplication can be even more efficiently done by reducing the number of partial product rows. This is made possible by radix 4 or radix 8 modified Booth multiplication techniques.

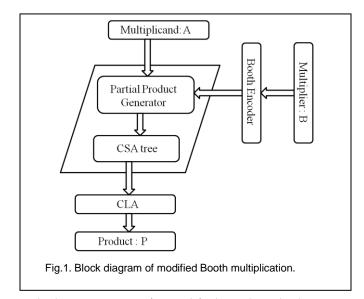

The basic structure of a modified Booth multiplier is given in figure 1. It has hardware structures for Booth encoder, partial product generator, the Carry save adder tree and the final Carry lookahead adder. The multiplier is recoded and encoded using the Booth encoder. Based on the Booth encoder output, the partial products are generated. The partial product rows are then added using the Carry save tree and the carry lookahead adder does the final addition.

The multiplication operation of two *n* bit signed numbers  $A = a_{n-1}a_{n-2}...a_0$  (multiplicand) and  $B = b_{n-1}b_{n-2}...b_0$  (multiplier) shall be considered. The numbers can be expressed in their two's complement as:

$A = -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i, \qquad B = -b_{n-1}2^{n-1} + \sum_{i=0}^{n-2} b_i 2^i \qquad (1)$

Multiplier recoding [10] is the process by which the multiplier is recoded such that reductions in the number of partial product rows are made possible depending on the recoded multiplier.

For modified Booth encoding, a "0" must always be concatenated to the right of *B*, and *n* should be even. By modified Booth encoding [12] which groups the bits of the multiplier into triplets, *B* can be expressed as

$$B = \sum_{i=0}^{2^{-1}} (-2b_{2i+1} + b_{2i} + b_{2i-1}) 2^{2i}$$

Table L summarizes the coding operation by equation (2)

Table I. summarizes the coding operation by equation (2).

Table I. Modified Booth encoding table.

| <i>b</i> <sub>2i+1</sub> | b <sub>2i</sub> | <i>b</i> <sub>2i-1</sub> | $b'_{i}$ | Negi | Twoi | Onei | Zeroi | Cor <sub>i</sub> |

|--------------------------|-----------------|--------------------------|----------|------|------|------|-------|------------------|

| 0                        | 0               | 0                        | 0        | 0    | 0    | 0    | 1     | 0                |

| 0                        | 0               | 1                        | +A       | 0    | 0    | 1    | 0     | 0                |

| 0                        | 1               | 0                        | +A       | 0    | 0    | 1    | 0     | 0                |

| 0                        | 1               | 1                        | +2A      | 0    | 1    | 0    | 0     | 0                |

| 1                        | 0               | 0                        | -2A      | 1    | 1    | 0    | 0     | 1                |

| 1                        | 0               | 1                        | -A       | 1    | 0    | 1    | 0     | 1                |

| 1                        | 1               | 0                        | -A       | 1    | 0    | 1    | 0     | 1                |

| 1                        | 1               | 1                        | 0        | 1    | 0    | 0    | 1     | 0                |

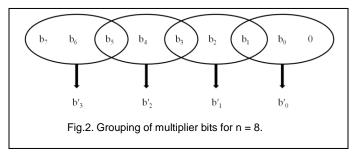

Figure 2. shows Grouping of multiplier bits for n = 8. It demonstrates how multiplier recoding is done. Here the operation to be performed is determined by b'<sub>i</sub>. The Booth encoder is designed based on the truth table given in table I. The input bits are the triplets which are taken as inputs for multiplier recoding. The operations to be performed are determined by the Booth encoder. The encoder outputs are used to choose one of multiple multiplicands -2*A*, -*A*, 0, *A* or 2*A* for generating each partial product row PP<sub>i</sub>.

Many real life applications related with digital signal processing systems use fixed width multipliers. In fixed width modified Booth multipliers, the n most significant output bits of the multiplier are kept and the least significant output bits are truncated hence making a multiplier giving *n* output bits for an  $n \times n$  multiplication. The previous works related to fixed width modified Booth multiplier includes multiplier designs using approximate carry generation by exhaustive simulation, approximate carry generation by statistical analysis, compensation circuits using constant scheme or the adaptive scheme etc. The recent work related with fixed width modified Booth multiplier uses a comparison based sorting network for compensation. In this paper, an error compensation circuit for the fixed-width modified Booth multiplier with higher accuracy and simpler hardware structure using simple logic gate is proposed. To obtain better performance with a simple error compensation circuit, Booth encoded outputs are utilized here to generate the error compensation value.

#### **3 PROPOSED FIXED WIDTH BOOTH MULTIPLIER**

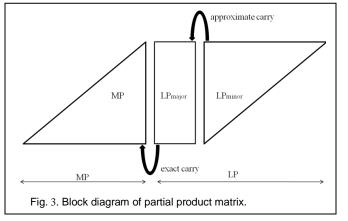

The block diagram of the partial product matrix for modified Booth multiplication is shown in figure 3. Partial products for modified Booth multiplier can be divided into *MP* and *LP* as shown in figure.

IJSER © 2013 http://www.ijser.org

The 2n-bit output product P can be expressed as, P = S MP + S LP(3)

To generate error compensation bias more efficiently, LP can be further divided into LP<sub>major</sub> and LP<sub>minor</sub>. From figure 3, notice that  $LP_{major}$  has a dominant effect on the carry signals generated from LP part since LP<sub>major</sub> has the largest weight in the LP part. Also, the generated partial products are directly dependent on the Booth encoder outputs. From figure 3, S\_LP can be expressed as,

$S\_LP = S\_LP_{major} + S\_LP_{minor}$

The outputs of the proposed Booth encoder can be designed using the Karnaugh map method, where the output bits are realized from the truth table given in table II. The truth table for the proposed Booth encoder is shown in table II.

(4)

| Table II  | Truth | table | for t | ho | nror | hason | Booth | encoder. |

|-----------|-------|-------|-------|----|------|-------|-------|----------|

| lable II. | muun  | lable | 101 t | ne | prot | Joseu | DOOUL | encouer. |

| 1 1                      |          |                          |              |      |      |                  |                   |       |

|--------------------------|----------|--------------------------|--------------|------|------|------------------|-------------------|-------|

| <i>b</i> <sub>2i+1</sub> | $b_{2i}$ | <i>b</i> <sub>2i-1</sub> | <i>b</i> ′ i | Negi | Twoi | One <sub>i</sub> | Zero <sub>i</sub> | Compi |

| 0                        | 0        | 0                        | 0            | 0    | 0    | 0                | 1                 | 0     |

| 0                        | 0        | 1                        | +A           | 0    | 0    | 1                | 0                 | 1     |

| 0                        | 1        | 0                        | +A           | 0    | 0    | 1                | 0                 | 1     |

| 0                        | 1        | 1                        | +2A          | 0    | 1    | 0                | 0                 | 1     |

| 1                        | 0        | 0                        | -2A          | 1    | 1    | 0                | 0                 | 1     |

| 1                        | 0        | 1                        | -A           | 1    | 0    | 1                | 0                 | 1     |

| 1                        | 1        | 0                        | -A           | 1    | 0    | 1                | 0                 | 1     |

| 1                        | 1        | 1                        | 0            | 1    | 0    | 0                | 1                 | 0     |

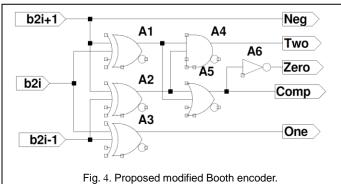

The proposed Booth encoder structure is shown in figure 4. It has an improvement in its design from the previous encoders that since the proposed encoder is used for fixed width modified Booth multiplication, the Cor<sub>i</sub> bits are not generated and used for partial product generation. This is because of the fact that in the proposed design, neither the LP<sub>minor</sub> partial product bits nor the Cor<sub>i</sub> bits are taken by the compensation circuit for producing the necessary compensation.

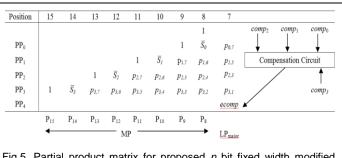

The partial product array for the proposed architecture is shoen in figure. A compensation value 'ecomp' is added as the approximate carry to the *LP*<sub>major</sub> such that it is been added with the retained adder cells and effective compensation is made possible. The sign extension scheme used here is the sign generate sign extension scheme.

Fig.5. Partial product matrix for proposed n bit fixed width modified Booth multiplier

## 3.2 Compensation Circuit

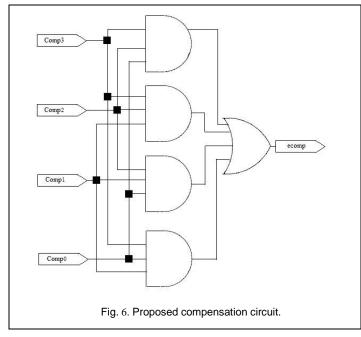

The compensation circuit proposed here is based on majority selection logic such that there will be a carry for any of two rows of the partial product being not completely zero. The PP<sub>3</sub> and PP4 rows need not be taken into consideration since there are no partial products in these rows which are to be considered. The design of the proposed compensation circuit can be got from the truth table given by table III.

Table III. Truth table for compensation circuit.

| Comp3 | Comp2 | Comp1 | Comp0 | ecomp |

|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 0     | 1     | 0     |

| 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 1     | 0     |

| 0     | 1     | 0     | 0     | 0     |

| 0     | 1     | 0     | 1     | 0     |

| 0     | 1     | 1     | 0     | 0     |

| 0     | 1     | 1     | 1     | 1     |

| 1     | 0     | 0     | 0     | 0     |

| 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     | 1     |

| 1     | 1     | 0     | 0     | 0     |

| 1     | 1     | 0     | 1     | 1     |

| 1     | 1     | 1     | 0     | 1     |

| 1     | 1     | 1     | 1     | 1     |

Karnaugh map reductions are made for the truth table. The equation using Karnaugh map reduction can be given as:  $ecomp = (Comp_3 . Comp_2 . Comp_0) + (Comp_3 . Comp_2 . Comp_1) +$  $(Comp_2. Comp_1. Comp_0) + (Comp_3. Comp_1. Comp_0)$ (5)

LISER © 2013 http://www.ijser.org International Journal of Scientific & Engineering Research Volume 4, Issue 8, August-2013 ISSN 2229-5518

The circuit implementation for the equation is shown in figure 6.

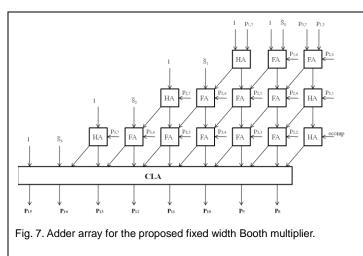

#### 3.3 Adder Arrray

The summand summation unit is processed using the carry saved adder (CSA) tree and the carry propogate adder (CPA). Figure 7. shows adder array for the proposed fixed width modified Booth multiplier. The summand matrix needs three CSA tree levels. Although the compensation vector must be applied to partial product row PP<sub>4</sub>, through careful arrangement the CSA tree level does not increase.

# **4** EXPERIMENTAL RESULTS

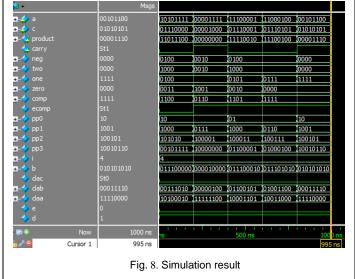

To compare the characteristics of fixed width modified Booth multipliers, the proposed circuit as well as the SC fixed width modified Booth multipliers was implemented in Verilog HDL. These fixed-width Booth multipliers were synthesized through utilizing Leonardo Spectrum LS2009a and Xilinx ISE 8.1. The implementation results including number of gates and critical path delay are compared. The simulation result is

Table IV. Synthesis report

|                       | Delay    | Number of gates |

|-----------------------|----------|-----------------|

| FWMBM in reference[1] | 25.651ns | 234             |

| Proposed FWMBM        | 22.428ns | 223             |

The proposed fixed width modified Booth multiplier can be considered to be showing better results.

# 5 CONCLUSION

Through this project, a high-accuracy fixed-width modified Booth multiplier has been proposed. In the proposed multiplier, the partial product matrix of Booth multiplication was modified such that the adder cells needed for the computation of the n least significant output bits of the multiplier are removed hence making significant hardware complexity reduction and power saving.

The Booth encoder structure particularly or fixed width multiplication is designed. In addition, a simplified compensation network using simple logic gates has been designed to realize the compensation function. Implementation results showed that the proposed fixed-width modified Booth multiplier can achieve reduction in the area as well as critical path delay when compared with the previous circuit using SC compensation.

#### REFERENCES

- K. Choi and M. Song, "Design of a high performance 32 × 32-bit multiplier with a novel sign select Booth encoder," in *Proc. IEEE Int. Symp. Circuits and Systems*, 2001, vol. 2, pp. 701–704.

- [2] F. Elguibaly, "A fast parallel multiplier-accumulator using the modified Booth algorithm," *IEEE Trans. Circuits Syst. II, Reg. Papers,* vol. 47, no. 9, pp. 902–908, Sep. 2000.

- [3] W.-C. Yeh and C.-W. Jen, "High-speed Booth encoded parallel

shown in figure 8.

International Journal of Scientific & Engineering Research Volume 4, Issue 8, August-2013 ISSN 2229-5518

multiplier design," IEEE Trans. Computers, vol. 49, no. 7, pp. 692–701, July 2000.

- [4] S. S. Kidambi, F. El-Guibaly, and A. Antoniou, "Area-efficient multipliers for digital signal processing applications," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 43, no. 2, pp. 90–94, Feb. 1996.

- [5] Y. C. Lim, "Single precision multiplier with reduced circuit complexity for signal processing applications," *IEEE Trans. Computer*, vol. 41, no.10, pp. 1333–1336, Oct. 1992.

- [6] J. M. Jou, S. R. Kuang, and R. D. Chen, "Design of low-error fixed width multipliers for DSP applications," *IEEE Trans. Circuits Syst. I, Exp. Briefs, vol. 46, no. 6, pp. 836–842, June 1999.*

- [7] L. D. Van, S. S.Wang, and W. S. Feng, "Design of the low error fixed width multiplier and its application," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 47, no. 10, pp. 1112–1118, Oct. 2000.

- [8] Y.-C. Liao, H.-C. Chang, and C.-W. Liu, "Carry estimation for two's complement fixed-width multipliers," in *Proc. IEEE Workshop Signal Processing Systems*, 2006, pp. 345–350.

- [9] S. J. Jou, M.-H. Tsai, and Y.-L. Tsao, "Low-error reduced-width Booth multipliers for DSP applications," *IEEE Trans. Circuits Syst. I, Fudam. Theory Appl.*, vol. 50, no. 11, pp. 1470–1474, Nov. 2003

- [10] K.-J. Cho, K.-C. Lee, J.-G. Chung, and K. K. Parhi, "Design of low error fixed-width modified Booth multiplier," *IEEE Trans. Very Large Scale Integration (VLSI) Syst., vol. 12, no. 5, pp. 522–531, May 2004.*

- [11] M.-A. Song, L.-D. Van, and S.-Y. Kuo, "Adaptive low-error fixedwidth Booth multipliers," *IEICE Trans. Fundamentals*, vol. E90-A, no.6, pp. 1180–1187, Jun. 2007.

- [12] Jiun-Ping Wang, Shiann-Rong Kuang, Member, IEEE, and Shish-Chang Liang, "High-Accuracy Fixed-Width Modified Booth Multipliers for Lossy Applications," *IEEE transactions on very large scale integration (VLSI) systems, vol. 19, no. 1,,* pp. 52–60, January 2011.

- [13] Andrew D. Booth, "A signed binary multiplication technique," Birkbeck college Electronic computer project, August 1951

- [14] E. de Angel and E. E. Swartzlander, Jr., "Low power parallel multipliers," in Workshop VLSI Signal Process., IX, 1996, pp. 199– 208.

- [15] M. J. Schulte and E. E. Swartzlander, Jr., "Truncated multiplication with correction constant," in *Proc. VLSI Signal Processing*, VI, New York, 1993, pp. 388–396.